August 2006

# NS16C2552/NS16C2752 Dual UART with 16-byte/64-byte FIFO's and up to 5 Mbit/s Data Rate

### 1.0 General Description

The NS16C2552 and NS16C2752 are dual channel Universal Asynchronous Receiver/Transmitter (DUART). The footprint and the functions are compatible to the PC16552D, while new features are added to the UART device. These features include low voltage support, 5V tolerant inputs, enhanced features, enhanced register set, and higher data rate

The two serial channels are completely independent of each other, except for a common CPU interface and crystal input. On power-up both channels are functionally identical to the PC16552D. Each channel can operate with on-chip transmitter and receiver FIFO's (in FIFO mode).

In the FIFO mode each channel is capable of buffering 16 bytes (for NS16C2552) or 64 bytes (for NS16C2752) of data in both the transmitter and receiver. The receiver FIFO also has additional 3 bits of error data per location. All FIFO control logic is on-chip to minimize system software overhead and maximize system efficiency.

To improve the CPU processing bandwidth, the data transfers between the DUART and the CPU can be done using DMA controller. Signaling for DMA transfers is done through two pins per channel (TXRDY and RXRDY). The RXRDY function is multiplexed on one pin with the OUT2 and BAUD-OUT functions. The configuration is through Alternate Function Register.

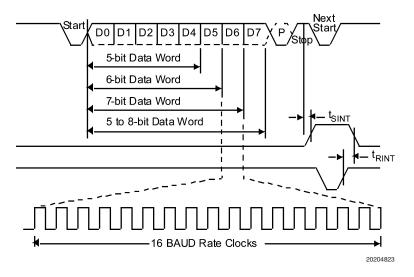

The fundamental function of the UART is converting between parallel and serial data. Serial-to-parallel conversion is done on the UART receiver and parallel-to-serial conversion is done on the transmitter. The CPU can read the complete status of each channel at any time. Status information reported includes the type and condition of the transfer operations being performed by the DUART, as well as any error conditions (parity, overrun, framing, or break interrupt).

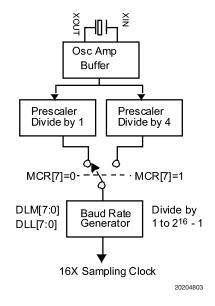

The NS16C2552 and NS16C2752 include one programmable baud rate generator for each channel. Each baud rate generator is capable of dividing the clock input by divisors of 1 to (2<sup>16</sup> - 1), and producing a 16X clock for driving the internal transmitter logic and for receiver sampling circuitry. The NS16C2552 and NS16C2752 have complete MODEM-control capability, and a processor-interrupt system. The interrupts can be programmed by the user to minimize the processing required to handle the communications link.

#### 2.0 Features

- Dual independent UART

- Up to 5 Mbits/s data transfer rate

- 2.97 V to 5.50 V operational Vcc

- 5 V tolerant I/Os in the entire supply voltage range

- Industrial Temperature: -40°C to 85°C

- Default registers are identical to the PC16552D

- NS16C2552/NS16C2752 is pin-to-pin compatible to NSC PC16552D, EXAR ST16C2552, XR16C2552, XR 16L2552, and Phillips SC16C2552B

- NS16C2752 is compatible to EXAR XR16L2752, and register compatible to Phillips SC16C752

- Auto Hardware Flow Control (Auto-CTS, Auto-RTS)

- Auto Software Flow Control (Xon, Xoff, and Xon-any)

- Fully programmable character length (5, 6, 7, or 8) with even, odd, or no parity, stop bit

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from the serial data

- Independently controlled and prioritized transmit and receive interrupts

- Complete line status reporting capabilities

- Line break generation and detection

- Internal diagnostic capabilities

- Loopback controls for communications link fault isolation

- Break, parity, overrun, framing error detection

- Programmable baud generators divide any input clock by 1 to (2<sup>16</sup> - 1) and generate the 16 X clock

- IrDA v1.0 wireless Infrared encoder/decoder

- DMA operation (TXRDY/RXRDY)

- Concurrent write to DUART internal register channels 1 and 2

- Multi-function output allows more package functions with fewer I/O pins

- 44-PLCC or 48-TQFP package

# **Table of Contents**

| 1.0 General Description                                 |     |

|---------------------------------------------------------|-----|

| 2.0 Features                                            |     |

| 3.0 System Block Diagram                                |     |

| 4.0 Connection Diagrams                                 | . 4 |

| 5.0 Pin Descriptions                                    | . 5 |

| 5.1 PARALLEL BUS INTERFACE                              | . 5 |

| 5.2 SERIAL IO INTERFACE                                 |     |

| 5.3 CLOCK AND RESET                                     |     |

| 5.4 POWER AND GROUND                                    |     |

| 6.0 Register Set                                        | 9   |

| 6.1 RECEIVE BUFFER REGISTER (RBR)                       |     |

| 6.2 TRANSMIT HOLDING REGISTER (THR)                     |     |

| 6.3 INTERRUPT ENABLE REGISTER (IER)                     |     |

| 6.4 INTERRUPT IDENTIFICATION REGISTER (IIR)             |     |

| 6.5 FIFO CONTROL REGISTER (FCR)                         | 14  |

| 6.6 LINE CONTROL REGISTER (LCR)                         | 16  |

| 6.7 MODEM CONTROL REGISTER (MCR)                        |     |

| 6.8 LINE STATUS REGISTER (LSR)                          |     |

| 6.9 MODEM STATUS REGISTER (MSR)                         |     |

| 6.10 SCRATCHPAD REGISTER (SCR)                          | 23  |

| 6.11 PROGRAMMABLE BAUD GENERATOR                        |     |

| 6.12 ALTERNATE FUNCTION REGISTER (AFR)                  |     |

| 6.13 DEVICE IDENTIFICATION REGISTER (ID)                |     |

| 6.14 ENHANCED FEATURE REGISTER (EFR)                    | 25  |

| 6.15 SOFTWARE FLOW CONTROL REGISTERS (SFR)              |     |

| 7.0 Operation and Configuration                         |     |

| 7.1 GEOGR INPOT                                         |     |

| 7.3 RECEIVER OPERATION                                  |     |

| 7.3.1 Receive in FIFO Mode                              |     |

| 7.3.2 Receive in non-FIFO Mode                          |     |

| 7.3.3 Receive Hardware Flow Control                     |     |

| 7.3.4 Receive Flow Control Interrupt                    |     |

| 7.5.4 TRANSMIT OPERATION                                |     |

| 7.4.1 Transmit in FIFO Mode                             |     |

| 7.4.2 Transmit in non-FIFO Mode                         |     |

| 7.4.3 Transmit Hardware Flow Control                    |     |

| 7.4.4 Transmit Flow Control Interrupt                   |     |

| 7.5 SOFTWARE XON/XOFF FLOW CONTROL                      | 31  |

| 7.6 SPECIAL CHARACTER DETECT                            | 31  |

| 7.7 SLEEP MODE                                          |     |

| 7.8 INTERNAL LOOPBACK MODE                              |     |

| 7.9 DMA OPERATION                                       |     |

| 7.10 INFRARED MODE                                      |     |

| 8.0 Design Notes                                        |     |

| 8.1 DEBUGGING HINTS                                     |     |

| 8.2 CLOCK FREQUENCY ACCURACY                            | 34  |

| 8.3 CRYSTAL REQUIREMENTS                                |     |

| 8.4 CONFIGURATION EXAMPLES                              | 35  |

| 8.4.1 Set Baud Rate                                     |     |

| 8.4.2 Configure Prescaler Output                        |     |

| 8.4.3 Set Xon and Xoff flow control                     |     |

| 8.4.4 Set Software Flow Control                         |     |

| 8.4.5 Configure Tx/Rx FIFO Threshold                    |     |

| 8.4.6 Tx and Rx Hardware Flow Control                   |     |

| 8.4.7 Tx and Rx DMA Control                             | 35  |

| 8.5 DIFFERENCES BETWEEN THE PC16552D AND NS16C2552/2752 |     |

| 8.6 NOTES ON TX FIFO OF NS16C2752                       |     |

| 9.0 Absolute Maximum Ratings                            |     |

| 10.0 DC and AC Specifications                           |     |

| 10.1 DC SPECIFICATIONS                                  |     |

| 10.2 CAPACITANCE                                        | 37  |

# Table of Contents (Continued)

| 10.3 AC SPECIFICATIONS   | 37 |

|--------------------------|----|

| 11.0 Timing Diagrams     | 39 |

| 12.0 Physical Dimensions | 42 |

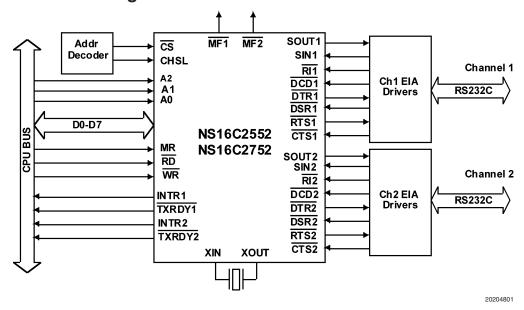

## 3.0 System Block Diagram

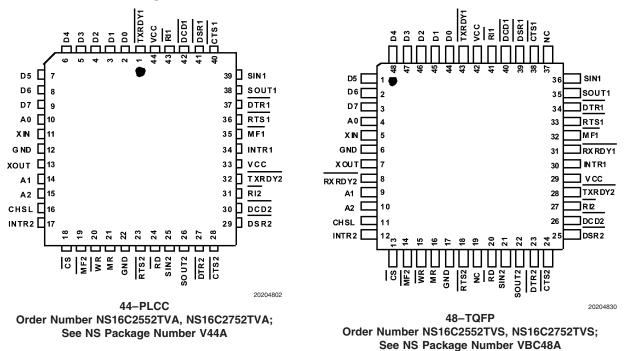

# 4.0 Connection Diagrams

# 5.0 Pin Descriptions

The NS16C2552/NS16C2752 pins are classified into the following interface categories.

- · Bus Interface

- Serial I/O Interface

- Clock and Reset

- Power supply and Ground pins

Serial channel number (1 or 2) is designated by a numerical suffix after each pin name. If a numerical suffix (1 or 2) is not associated with the pin name, the information applies to both channels.

The I/O types are as follows:

Type: I Input

Type: O Output

Type: IO\_Z TRI-STATE I/O

#### **5.1 PARALLEL BUS INTERFACE**

| Signal |      | PLCC  | TQFP  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | Туре | Pin # | Pin # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D7     |      | 9     | 3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D6     |      | 8     | 2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D5     |      | 7     | 1     | Data Bus:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| D4     | IO Z | 6     | 48    | Data bus comprises eight TRI-STATE input/output lines. The bus provides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D3     | 10_2 | 5     | 47    | bidirectional communications between the UART and the CPU. Data, control words,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D2     |      | 4     | 46    | and status information are transferred via the D <sub>7</sub> -D <sub>0</sub> Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D1     |      | 3     | 45    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| D0     |      | 2     | 44    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A2     | I    | 15    | 10    | Register Addresses:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A1     |      | 14    | 9     | Address signals connected to these 3 inputs select a DUART register for the CPU to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A0     |      | 10    | 4     | read from or write to during data transfer. <i>Table 1</i> shows the registers and their addresses. Note that the state of the Divisor Latch Access Bit (DLAB), which is the most significant bit of the Line Control Register, affects the selection of certain DUART registers. The DLAB must be set high by the system software to access the Baud Generator Divisor Latches and the Alternate Function Register.                                                                                                                                                                                                                                                               |

| CS     | I    | 18    | 13    | Chip Select: When $\overline{CS}$ is low, the chip is selected. This enables communication between the DUART and the CPU. Valid chip select should stabilize according to the $t_{AW}$ parameter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CHSL   | I    | 16    | 11    | Channel Select:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |      |       |       | CHSL directs the address and data information to the selected serial channel. ( <i>Table 1</i> )  1 = channel 1 is selected.  0 = channel 2 is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

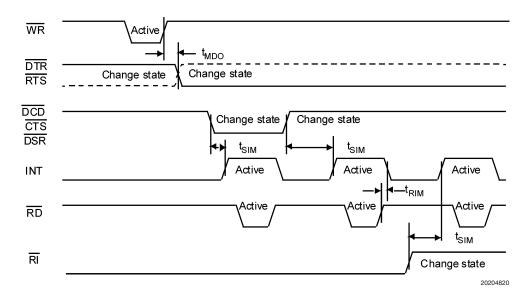

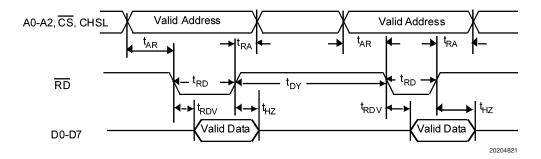

| RD     | I    | 24    | 20    | IO Read:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

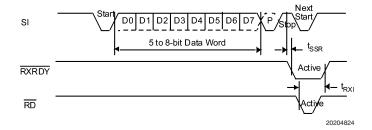

|        |      |       |       | The register data is placed on the D0 - D7 on the falling edge of $\overline{RD}$ . The CPU can read status information or data from the selected DUART register on the rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

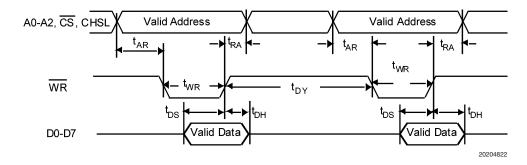

| WR     | I    | 20    | 15    | IO Write:  On the falling edge of WR, data is placed on the D0 - D7. On the rising edge, the data is latched into the selected DUART register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RXRDY1 | 0    | N/A   | 31    | UART Receive-ready: The receiver DMA signaling is available through this pin which                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RXRDY2 |      |       | 8     | is a seperate pin on the TQFP package, while on the PLCC package it is available through the $\overline{\text{MF}}$ pins (19, 35). When operating in the FIFO mode, the CPU selects one of two types of DMA transfer via FCR[3]. When operating in the 16450 Mode, only DMA mode 0 is available. Mode 0 supports single transfer DMA (and a transfer is usually made between CPU bus cycles). Mode 1 supports multi-transfer DMA where multiple transfers are made continuously until the Rx FIFO is empty. Details regarding the active and inactive states of this signal are described in <i>Section 6.5 FIFO CONTROL REGISTER (FCR)</i> and <i>Section 7.9 DMA OPERATION</i> . |

# 5.0 Pin Descriptions (Continued)

| Signal |      | PLCC  | TQFP  |                                                                                           |

|--------|------|-------|-------|-------------------------------------------------------------------------------------------|

| Name   | Туре | Pin # | Pin # | Description                                                                               |

| TXRDY1 | 0    | 1     | 43    | UART Transmit-ready:                                                                      |

| TXRDY2 |      | 32    | 28    | Transmitter DMA signaling is available through this pin. When operating in the FIFO       |

|        |      |       |       | mode, the CPU selects one of two types of DMA transfer via FCR[3]. When operating         |

|        |      |       |       | in the 16450 Mode, only DMA mode 0 is allowed. Mode 0 supports single transfer            |

|        |      |       |       | DMA (and a transfer is usually made between CPU bus cycles). Mode 1 supports              |

|        |      |       |       | multi-transfer DMA where multiple transfers are made continuously until the Tx FIFO       |

|        |      |       |       | is full. Details regarding the active and inactive states of this signal are described in |

|        |      |       |       | Section 6.5 FIFO CONTROL REGISTER (FCR) and Section 7.9 DMA OPERATION.                    |

| INTR1  | 0    | 34    | 30    | Interrupt Output:                                                                         |

| INTR2  |      | 17    | 12    | INTR goes high whenever any one of the following interrupt types has an active high       |

|        |      |       |       | condition and is enabled via the IER: Receiver Error Flag; Received Data Available:       |

|        |      |       |       | time-out (FIFO Mode only); Transmitter Holding Register Empty; MODEM Status; and          |

|        |      |       |       | hardware and software flow control. The INTR signal is reset low upon the                 |

|        |      |       |       | appropriate interrupt service or a Master Reset operation.                                |

### **5.2 SERIAL IO INTERFACE**

| Signal |      | PLCC  | TQFP  |                                                                                                                          |

|--------|------|-------|-------|--------------------------------------------------------------------------------------------------------------------------|

| Name   | Туре | Pin # | Pin # | Description                                                                                                              |

| SOUT1  | 0    | 38    | 35    | UART Serial Data Out:                                                                                                    |

| SOUT2  |      | 26    | 22    | UART transmit data output or infrared data output. The SOUT signal is set to logic 1                                     |

|        |      |       |       | upon reset or idle in the UART mode when MCR[6]=0. The SOUT signal transitions to                                        |

|        |      |       |       | logic 0 (idle state of IrDA mode) in the infrared mode when MCR[6]=1.                                                    |

|        |      |       |       | Note: SOUT1 and SOUT2 can not be reset to IrDA mode.                                                                     |

| SIN1   | 1    | 39    | 36    | UART Serial Data In:                                                                                                     |

| SIN2   |      | 25    | 21    | UART receive data input or infrared data input. The SIN should be idling in logic 1 in                                   |

|        |      |       |       | the UART mode. The SIN should be idling in logic 0 in the infrared mode. The SIN                                         |

|        |      |       |       | should be pulled high through a 10K resistor if not used.                                                                |

| RTS1   | 0    | 36    | 33    | UART Request-to-send:                                                                                                    |

| RTS2   |      | 23    | 18    | When low, RTS informs the remote link partner that it is ready to receive data. The                                      |

|        |      |       |       | RTS output signal can be set to an active low by writing "1" to MCR[1]. The RTS                                          |

|        |      |       |       | output can also be configured in auto hardware flow control based on FIFO trigger                                        |

|        |      |       |       | level. This pin stays logic 1 upon reset or idle (i.e., between data transfers). Loop                                    |

|        |      |       |       | mode operation holds this signal in its inactive state.                                                                  |

| DTR1   | 0    | 37    | 34    | UART Data-terminal-ready:                                                                                                |

| DTR2   |      | 27    | 23    | When low, DTR informs the remote link partner that the UART is ready to establish a                                      |

|        |      |       |       | communications link. The DTR output signal can be set to an active low by writing "1"                                    |

|        |      |       |       | to MCR[0]. This pin stays at logic 1 upon reset or idle. Loop mode operation holds this                                  |

|        |      |       |       | signal to its inactive state.                                                                                            |

| CTS1   |      | 40    | 38    | UART Clear-to-send:                                                                                                      |

| CTS2   |      | 28    | 24    | When low, CTS indicates that the remote link partner is ready to receive data. The                                       |

|        |      |       |       | CTS signal is a modem status input and can be read for the appropriate channel in                                        |

|        |      |       |       | MSR[4]. This bit reflects the complement of the CTS signal. MSR[0] indicates whether                                     |

|        |      |       |       | the CTS input has changed state since the previous read of the MSR. CTS can also                                         |

|        |      |       |       | be configured to perform auto hardware flow control.                                                                     |

|        |      |       |       | Note: Whenever the CTS bit of the MSR changes state, an interrupt is generated if the MODEM Status Interrupt is enabled. |

# 5.0 Pin Descriptions (Continued)

| Signal       |      | PLCC     | TQFP     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|------|----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name         | Туре | Pin #    | Pin #    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DSR1<br>DSR2 | I    | 41<br>29 | 39<br>25 | UART Data-set-ready: When low, DSR indicates that the remote link partner is ready to establish the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |      |          |          | communications link. The $\overline{\text{DSR}}$ signal is a MODEM status input and can be read for the appropriate channel in MSR[5]. This bit reflects the complement of the $\overline{\text{DSR}}$ signal. MSR[1] indicates whether the $\overline{\text{DSR}}$ input has changed state since the previous read of the MODEM Status Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |      |          |          | Note: Whenever the DSR bit of the MSR changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DCD1         | I    | 42       | 40       | UART Data-carrier-detect:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DCD2         |      | 30       | 26       | When low, $\overline{DCD}$ indicates that the data carrier has been detected by the remote link partner. The $\overline{DCD}$ signal is a MODEM status input and can be read for the appropriate channel in MSR[7]. This bit reflects the complement of the $\overline{DCD}$ signal. MSR[3] indicates if the $\overline{DCD}$ input has changed state since the previous reading of the MODEM Status Register. $\overline{DCD}$ has no effect on the receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |      |          |          | Note: Whenever the DCD bit of the MSR changes state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RI1          | I    | 43       | 41       | UART Ring-detector:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RI2          |      | 31       | 27       | When low, $\overline{RI}$ indicates that a telephone ringing is active. The $\overline{RI}$ signal is a MODEM status input and can be read for the appropriate channel in MSR[6]. This bit reflects the complement of the $\overline{RI}$ signal. MSR[2] indicates whether the $\overline{RI}$ input signal has changed state from low to high since the previous reading of the MSR.  Note: Whenever the $\overline{RI}$ bit of the MSR changes from a high to a low state, an interrupt is generated if the MODEM Status Interrupt is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MF1          | 0    | 35       | 32       | UART Multi-function Pin:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MF2          |      | 19       | 14       | MF can be programmed for any one of three signal functions OUT2, BAUDOUT or RXRDY. Bits 2 and 1 of the Alternate Function Register select which output signal will be present on this pin. OUT2 is the default signal and it is selected immediately after master reset or power-up.  The OUT2 can be set active low by programming bit 3 (OUT2) of the MCR to a logic 1. A Master Reset operation sets this signal to its inactive (high) state. Loop Mode holds this signal in its inactive state.  The BAUDOUT signal is the 16X clock output that drives the transmitter and receiver logic of the associated serial channel. This signal is the result of the XIN clock divided by the value in the Divisor Latch Registers. The BAUDOUT signal for each channel is internally connected to provide the receiver clock (formerly RCLK on the PC16550D). The RXRDY signal can be used to request a DMA transfer of data from the RCVR FIFO. Details regarding the active and inactive states of this signal are described in Section 6.5 FIFO CONTROL REGISTER (FCR) and Section 7.9 DMA OPERATION. |

# 5.0 Pin Descriptions (Continued)

### 5.3 CLOCK AND RESET

| Signal<br>Name | Туре | PLCC<br>Pin # | TQFP<br>Pin # | Description                                                                                                                                    |

|----------------|------|---------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

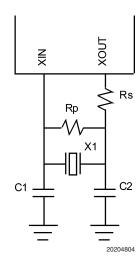

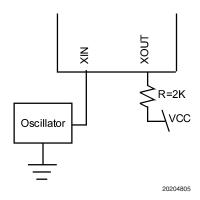

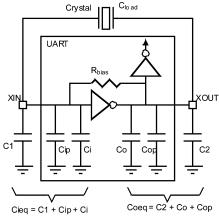

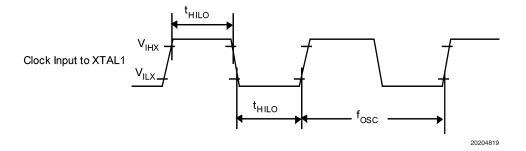

| XIN            | I    | 11            | 5             | External Crystal Input:                                                                                                                        |

|                |      |               |               | XIN input is used in conjunction with XOUT to form a feedback circuit for the baud rate generator's oscillator. If a clock signal is generated |

|                |      |               |               | off-chip, then it should drive the baud rate generator through this pin.                                                                       |

|                |      |               |               | Refer to Section 7.1 CLOCK INPUT.                                                                                                              |

| XOUT           | 0    | 13            | 7             | External Crystal Output:                                                                                                                       |

|                |      |               |               | XOUT output is used in conjunction with XIN to form a feedback circuit                                                                         |

|                |      |               |               | for the baud rate generator's oscillator. If the clock signal is generated                                                                     |

|                |      |               |               | off-chip, then this pin is unused. Refer to Section 7.1 CLOCK INPUT.                                                                           |

| MR             | I    | 21            | 16            | Master Reset:                                                                                                                                  |

|                |      |               |               | When MR input is high, it clears all the registers including Tx and Rx                                                                         |

|                |      |               |               | serial shift registers (except the Receiver Buffer, Transmitter Holding,                                                                       |

|                |      |               |               | and Divisor Latches). The output signals, such as $\overline{\text{OUT2}}$ , $\overline{\text{RTS}}$ , $\overline{\text{DTR}}$ ,               |

|                |      |               |               | INTR, and SOUT are also affected by an active MR input. (Refer to                                                                              |

|                |      |               |               | Table 26 and Section 7.2 RESET).                                                                                                               |

#### **5.4 POWER AND GROUND**

| Signal |      | PLCC  | TQFP  |                                                    |

|--------|------|-------|-------|----------------------------------------------------|

| Name   | Туре | Pin # | Pin # | Description                                        |

| VCC    | I    | 33    | 29    | V <sub>cc</sub> :                                  |

|        |      | 44    | 42    | +2.97V to +5.5V supply.                            |

| GND    | I    | 12    | 6     | GND:                                               |

|        |      | 22    | 17    | Device ground reference.                           |

| NC     | I    | N/A   | 19    | No Connection:                                     |

|        |      |       | 37    | These pins are only available on the TQFP package. |

# 6.0 Register Set

There are two identical register sets, one for each channel, in the DUART. All register descriptions in this section apply to the register sets in both channels.

To clarify the descriptions of transmission and receiving operations, the nomenclatures through out this documentation are as follows:

- Frame Refers to all the bits between Start and Stop.

- Character or word The payload of a frame, between 5 to 8 bits.

- "!=" Not equal to.

- Res Reserved bit.

The address and control pins to register selection is summarized in *Table 1*.

**TABLE 1. Basic Register Addresses**

|                       | DLAB1                           | CHSL                       | A2                                   | A1                         | A0                              | Register                                                                                                                                                   |

|-----------------------|---------------------------------|----------------------------|--------------------------------------|----------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | 0                               | 1                          | 0                                    | 0                          | 0                               | Receive Buffer (Read), Transmitter Holding Register (Write)                                                                                                |

|                       | 0                               | 1                          | 0                                    | 0                          | 1                               | Interrupt Enable                                                                                                                                           |

| С                     | 0                               | 1                          | 0                                    | 1                          | 0                               | Interrupt Identification (Read)                                                                                                                            |

| H                     | 0                               | 1                          | 0                                    | 1                          | 0                               | FIFO Control (Write)                                                                                                                                       |

| A                     | Х                               | 1                          | 0                                    | 1                          | 1                               | Line Control                                                                                                                                               |

| N<br>N                | Х                               | 1                          | 1                                    | 0                          | 0                               | Modem Control                                                                                                                                              |

| E                     | Х                               | 1                          | 1                                    | 0                          | 1                               | Line Status (Read)                                                                                                                                         |

| -                     | Х                               | 1                          | 1                                    | 1                          | 0                               | Modem Status (Read)                                                                                                                                        |

| 1                     | Х                               | 1                          | 1                                    | 1                          | 1                               | Scratchpad                                                                                                                                                 |

|                       | 1                               | 1                          | 0                                    | 0                          | 0                               | Divisor Latch (Least Significant Byte)                                                                                                                     |

|                       | 1                               | 1                          | 0                                    | 0                          | 1                               | Divisor Latch (Most Significant Byte)                                                                                                                      |

|                       | 1                               | 1                          | 0                                    | 1                          | 0                               | Alternate Function                                                                                                                                         |

|                       | DLAB1                           | CHSL                       | A2                                   | A1                         | A0                              | Register                                                                                                                                                   |

|                       |                                 |                            |                                      |                            |                                 |                                                                                                                                                            |

|                       | 0                               | 0                          | 0                                    | 0                          | 0                               | Receive Buffer (Read), Transmitter Holding Register                                                                                                        |

|                       | 0                               | 0                          | 0                                    | 0                          | 0                               | Receive Buffer (Read), Transmitter Holding Register (Write)                                                                                                |

| С                     | 0                               | 0                          | 0                                    | 0                          | 1                               | , , ,                                                                                                                                                      |

| C<br>H                |                                 | -                          |                                      |                            | -                               | (Write)                                                                                                                                                    |

|                       | 0                               | 0                          | 0                                    | 0                          | 1                               | (Write) Interrupt Enable                                                                                                                                   |

| Н                     | 0                               | 0                          | 0                                    | 0                          | 1 0                             | (Write) Interrupt Enable Interrupt Identification (Read)                                                                                                   |

| H<br>A                | 0 0                             | 0 0                        | 0 0 0                                | 0 1 1                      | 1 0 0                           | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write)                                                                              |

| H<br>A<br>N           | 0<br>0<br>0<br>x                | 0 0 0 0                    | 0<br>0<br>0<br>0                     | 0<br>1<br>1<br>1           | 1<br>0<br>0                     | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write) Line Control                                                                 |

| H<br>A<br>N<br>N<br>E | 0<br>0<br>0<br>x<br>x           | 0<br>0<br>0<br>0           | 0<br>0<br>0<br>0                     | 0 1 1 1 0                  | 1<br>0<br>0<br>1                | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write) Line Control Modem Control                                                   |

| H<br>A<br>N<br>N      | 0<br>0<br>0<br>x<br>x<br>x      | 0<br>0<br>0<br>0<br>0      | 0<br>0<br>0<br>0<br>0                | 0<br>1<br>1<br>1<br>0<br>0 | 1<br>0<br>0<br>1<br>0           | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write) Line Control Modem Control Line Status (Read)                                |

| H<br>A<br>N<br>N<br>E | 0<br>0<br>0<br>x<br>x<br>x<br>x | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>1<br>1      | 0<br>1<br>1<br>1<br>0<br>0 | 1<br>0<br>0<br>1<br>0<br>1<br>0 | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write) Line Control Modem Control Line Status (Read) Modem Status (Read)            |

| H<br>A<br>N<br>N<br>E | 0<br>0<br>0<br>x<br>x<br>x<br>x | 0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>1<br>1<br>1<br>1 | 0<br>1<br>1<br>1<br>0<br>0 | 1<br>0<br>0<br>1<br>0<br>1<br>0 | (Write) Interrupt Enable Interrupt Identification (Read) FIFO Control (Write) Line Control Modem Control Line Status (Read) Modem Status (Read) Scratchpad |

## TABLE 2. NS16C2552 Register Summary

|         |     | I       |         |          | IDLL 2. NO | 1002002  | riogiotoi | - Cummury     |          |             |

|---------|-----|---------|---------|----------|------------|----------|-----------|---------------|----------|-------------|

| Reg     |     |         |         |          |            |          |           |               |          |             |

| Addr    | RD/ |         |         |          |            |          |           |               |          | _           |

| A2-A0   | WR  | BIT 7   | BIT 6   | BIT 5    | BIT 4      | BIT 3    | BIT 2     | BIT 1         | BIT 0    | Comment     |

|         |     |         |         |          | · -        |          |           | ult Values Up |          |             |

| RBR     | R/W | Data7   | Data6   | Data5    | Data4      | Data3    | Data2     | Data1         | Data0    |             |

| THR     |     |         |         |          |            |          |           |               |          |             |

| 0x0     |     |         |         |          |            |          |           |               |          |             |

| Default |     | Х       | Х       | Х        | Х          | Х        | Х         | Х             | Х        |             |

| IER     | R/W | CTS Int | RTS     | Xoff Int | Sleep Md   | Modem    | RX        | Tx Empty      | Rx       |             |

| 0x1     |     | Ena     | Int     | Ena      | Ena        | Stat Int | Line      | Int Ena       | Data Int |             |

|         |     |         | Ena     |          |            | Ena      | Stat      |               | Ena      |             |

|         |     |         |         |          |            |          | Int       |               |          |             |

|         |     |         |         |          |            |          | Ena       |               |          |             |

| Default |     | 0       | 0       | 0        | 0          | 0        | 0         | 0             | 0        | LCR[7] = 0  |

| IIR     | R   | FIFOs   | FIFOs   | INT      | INT Src    | INT      | INT       | INT Src       | INT Src  |             |

| 0x2     |     | Ena     | Ena     | Src      | Bit 4      | Src      | Src       | Bit 1         | Bit 0    |             |

|         |     |         |         | Bit 5    |            | Bit 3    | Bit 2     |               |          |             |

| Default |     | 0       | 0       | 0        | 0          | 0        | 0         | 0             | 1        |             |

| FCR     | W   | RX      | RX      | Tx       | Tx FIFO    | DMA      | Tx        | Rx FIFO       | FIFOs    |             |

| 0x2     |     | FIFO    | FIFO    | FIFO     | Trigger    | Md       | FIFO      | Reset         | Ena      |             |

|         |     | Trigger | Trigger | Trigger  | (2752)     | Ena      | Reset     |               |          |             |

|         |     |         |         | (2752)   |            |          |           |               |          |             |

| Default |     | 0       | 0       | 0        | 0          | 0        | 0         | 0             | 0        |             |

| LCR     | R/W | Divisor | Set Tx  | Set      | Even       | Parity   | Stop      | Word          | Word     |             |

| 0x3     |     | Ena     | Break   | Parity   | Parity     | Ena      | Bits      | Length        | Length   |             |

|         |     |         |         |          |            |          |           | Bit 1         | Bit 0    |             |

| Default |     | 0       | 0       | 0        | 0          | 0        | 0         | 0             | 0        |             |

| MCR     | R/W | Clk Div | IR Md   | Xon      | Internal   | OUT2     | OUT1      | RTS           | DTR      |             |

| 0x4     |     | Sel     | Ena     | Any      | Loopbk     |          |           | Output        | Output   |             |

|         |     |         |         |          | Ena        |          |           | Control       | Control  |             |

| Default |     | 0       | 0       | 0        | 0          | 0        | 0         | 0             | 0        |             |

| LSR     | R   | Rx      | THR &   | THR E    | Rx         | Rx       | Rx        | Rx Overrun    | Rx       |             |

| 0x5     |     | FIFO    | TSR     | mpty     | Break      | Frame    | Parity    | Error         | Data     |             |

|         |     | Gbl Err | Empty   |          |            | Error    | Error     |               | Ready    | LODILONDE   |

| Default |     | 0       | 1       | 1        | 0          | 0        | 0         | 0             | 0        | LCR != 0xBF |

| MSR     | R   | DCD     | RI      | DSR      | CTS        | Delta    | Delta     | Delta         | Delta    |             |

| 0x6     |     | Input   | Input   | Input    | Input      | DCD      | RI        | DSR           | CTS      |             |

| Default |     | DCD     | RI      | DSR      | CTS        | 0        | 0         | 0             | 0        |             |

| SCR     | R/W | SCR     | SCR     | SCR      | SCR        | SCR      | SCR       | SCR           | SCR      |             |

| 0x7     |     | Bit 7   | Bit 6   | Bit 5    | Bit 4      | Bit 3    | Bit 2     | Bit 1         | Bit 0    |             |

| Default |     | 1       | 1       | 1        | 1          | 1        | 1         | 1             | 1        |             |

|         |     |         |         |          |            |          |           |               |          |             |

TABLE 2. NS16C2552 Register Summary (Continued)

|                             |     |        |         |         |          |          |           | , (           | /       |             |

|-----------------------------|-----|--------|---------|---------|----------|----------|-----------|---------------|---------|-------------|

| Reg<br>Addr                 | RD/ |        |         |         |          |          |           |               |         |             |

| A2-A0                       | WR  | BIT 7  | BIT 6   | BIT 5   | BIT 4    | BIT 3    | BIT 2     | BIT 1         | BIT 0   | Comment     |

| Baud Rate Generator Divisor |     |        |         |         |          |          |           |               |         |             |

| DLL                         | R/W | DLL    | DLL     | DLL     | DLL      | DLL      | DLL       | DLL           | DLL     |             |

| 0x0                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   |             |

| Default                     |     | Х      | Х       | Х       | Х        | Х        | Х         | Х             | Х       |             |

| DLM                         | R/W | DLM    | DLM     | DLM     | DLM      | DLM      | DLM       | DLM           | DLM     |             |

| 0x1                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   | LCR[7] = 1  |

| Default                     |     | Х      | Х       | Х       | Х        | Х        | Х         | Х             | Х       | LCR! 0xBF   |

| AFR                         | R/W | Rsrvd  | Rsrvd   | Rsrvd   | Rsrvd    | Rsrvd    | RXRDY     | BAUDOUT       | Con-    |             |

|                             |     |        |         |         |          |          |           |               | current |             |

| 0x2                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Sel       | Sel           | WR      |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

| DREV                        | R   | ID     | ID      | ID      | ID       | DREV     | DREV      | DREV          | DREV    | LCR[7] = 1  |

| 0x0                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   | LCR != 0xBF |

|                             |     |        |         |         |          |          |           |               |         | DLL = 0x00  |

|                             |     |        |         |         |          |          |           |               |         | DLM = 0x00  |

|                             |     |        |         |         |          | hanced I | Registers |               |         |             |

| EFR                         | R/W | Auto   | Auto    | Special | IER[7:4] | SW       | SW        | SW Flow       | SW      |             |

| 0x2                         |     | CTS    | RTS     | Char    | IIR[5:4] | Flow     | Flow      | Control Bit 1 | Flow    |             |

|                             |     | Ena    | Ena     | Sel     | FCR[5:4] | Control  | Control   |               | Control |             |

|                             |     | _      | _       | _       | MCR[7:5] | Bit 3    | Bit 2     | _             | Bit 0   |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

| XON1                        | R/W | XON1   | XON1    | XON1    | XON1     | XON1     | XON1      | XON1          | XON1    |             |

| 0x4                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

| XON2                        | R/W | XON2   | XON2    | XON2    | XON2     | XON2     | XON2      | XON2          | XON2    | LCR = 0xBF  |

| 0x5                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

| XOFF1                       | R/W | XOFF1  | XOFF1   | XOFF1   | XOFF1    | XOFF1    | XOFF1     | XOFF1         | XOFF1   |             |

| 0x6                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

| XOFF2                       | R/W | XOFF2  | XOFF2   | XOFF2   | XOFF2    | XOFF2    | XOFF2     | XOFF2         | XOFF2   |             |

| 0x7                         |     | Bit 7  | Bit 6   | Bit 5   | Bit 4    | Bit 3    | Bit 2     | Bit 1         | Bit 0   |             |

| Default                     |     | 0      | 0       | 0       | 0        | 0        | 0         | 0             | 0       |             |

|                             |     | Legend | Bit     |         |          |          |           |               |         |             |

|                             |     |        | Name    |         |          |          |           |               |         |             |

|                             |     |        | Default |         |          |          |           |               |         |             |

| 1                           |     | I      | Value   |         |          |          |           |               |         |             |

The Nomenclature of register descriptions:

- Register name, address, register bit, and value example:

FCR 0x2.7:6 = 2'b11 bits 6 and 7 of FCR are both 1.

Alternative description: FCR[7:6] = 2'b11.

- 'b binary number.

- 'h hex number.

- 0xNN hex number.

n'bN - n is the number of bits; N is the bit value. Example 8'b01010111 = 8'h57 = 0x57.

#### 6.1 RECEIVE BUFFER REGISTER (RBR)

The receiver section contains an 8-bit Receive Shift Register (RSR) and a 16 (or 64)-byte FIFO that can be accessed through Receive Buffer Register (RBR).

#### TABLE 3. RBR (0x0)

| Bit | Bit Name | R/W Def | Description                                              |  |  |  |

|-----|----------|---------|----------------------------------------------------------|--|--|--|

| 7:0 | RBR Data | R       | Receive Buffer Register                                  |  |  |  |

|     |          | 0xXX    | Rx FIFO data.                                            |  |  |  |

|     |          |         | Note: This register value does not change upon MR reset. |  |  |  |

#### 6.2 TRANSMIT HOLDING REGISTER (THR)

This register holds the byte-wide transmit data (THR). This is a write-only register.

#### TABLE 4. THR (0x0)

| Bit | Bit Name | R/W Def | Description                                              |

|-----|----------|---------|----------------------------------------------------------|

| 7:0 | THR Data | W       | Transmit Holding Register                                |

|     |          | 0xXX    | Tx FIFO data.                                            |

|     |          |         | Note: This register value does not change upon MR reset. |

#### **6.3 INTERRUPT ENABLE REGISTER (IER)**

This register enables eight types of interrupts for the corresponding serial channel. Each interrupt source can individually activate the interrupt (INTR) output signal. Setting the bits of the IER to a logic 1 unmasks the selected interrupt(s). Similarly, the interrupt can be masked off by resetting bits 0 through 7 of the Interrupt Enable Register (IER). If not de-

sired to be used, masking an interrupt source prevents it from going active in the IIR and activating the INTR output signal. While interrupt sources are masked off, all system functions including the Line Status and MODEM Status still operate in their normal manner. *Table 5* shows the contents of the IER.

#### TABLE 5. IER (0x1)

|     |              | R/W |                                                                                                                 |

|-----|--------------|-----|-----------------------------------------------------------------------------------------------------------------|

| Bit | Bit Name     | Def | Description                                                                                                     |

| 7   | CTS Int Ena  | R/W | CTS Input Interrupt Enable                                                                                      |

|     |              | 0   | 1 = Enable the $\overline{\text{CTS}}$ to generate interrupt at low to high transition. Requires EFR 0x2.4 = 1. |

|     |              | ĺ   | $0 = Disable the \overline{CTS}$ interrupt (default).                                                           |

| 6   | RTS Int Ena  | R/W | RTS Output Interrupt Enable                                                                                     |

|     |              | 0   | 1 = Enable the $\overline{RTS}$ to generate interrupt at low to high transition. Requires EFR 0x2.4 = 1.        |

|     |              |     | 0 = Disable the RTS interrupt (default).                                                                        |

| 5   | Xoff Int Ena | R/W | Xoff Input Interrupt Enable                                                                                     |

|     |              | 0   | 1 = Enable the software flow control character Xoff to generate interrupt. Requires EFR                         |

|     |              |     | 0x2.4 = 1.                                                                                                      |

|     |              | l   | 0 = Disable the Xoff interrupt (default).                                                                       |

| 4   | Sleep Mode   | R/W | Sleep Mode Enable                                                                                               |

|     | Ena          | 0   | 1 = Enable the Sleep Mode for the respective channel. Requires EFR 0x2.4 = 1.                                   |

|     | !            | İ   | 0 = Disable Sleep Mode (default).                                                                               |

| 3   | Mdm Stat Int | R/W | Modem Status Interrupt Enable                                                                                   |

|     | Ena          | 0   | 1 = Enable the Modem Status Register interrupt.                                                                 |

|     |              | l   | 0 = Disable the Modem Status Register interrupt (default).                                                      |

| 2   | Rx Line Stat | R/W | Receive Line Status Interrupt Enable                                                                            |

|     | Int Ena      | 0   | An interrupt can be generated when any of the LSR bits 0x5.4:1=1. LSR 0x5.1 generates                           |

|     |              | l   | an interrupt as soon as an overflow frame is received. LSR 0x5.4:2 generate an interrupt                        |

|     |              |     | when there is read error from FIFO.                                                                             |

|     |              | ĺ   | 1 = Enable the receive line status interrupt.                                                                   |

|     |              |     | 0 = Disable the receive line status interrupt (default).                                                        |

| 1   | Tx_Empty Int | R/W | Tx Holding Reg Empty Interrupt Enable                                                                           |

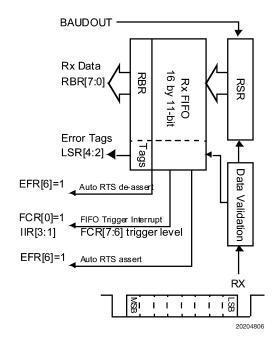

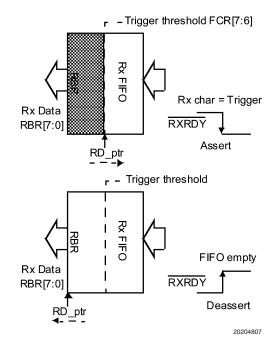

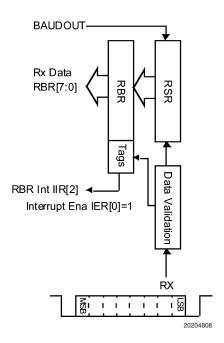

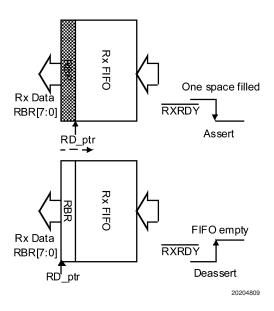

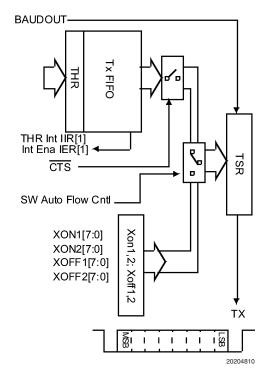

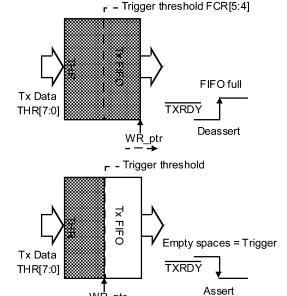

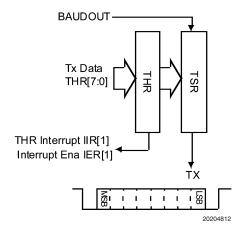

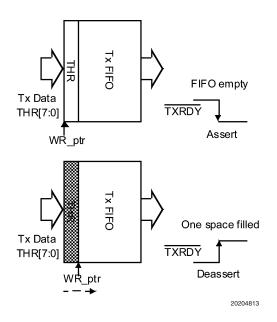

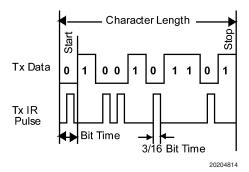

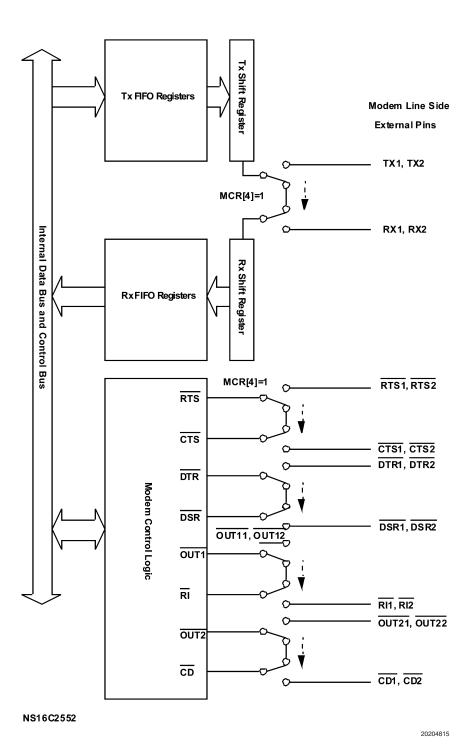

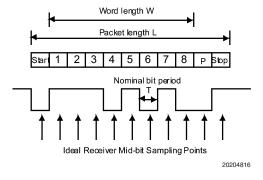

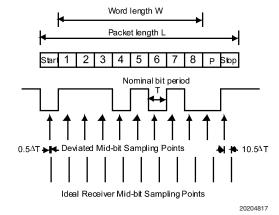

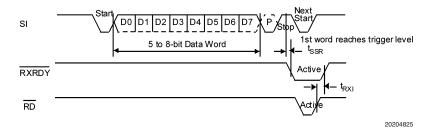

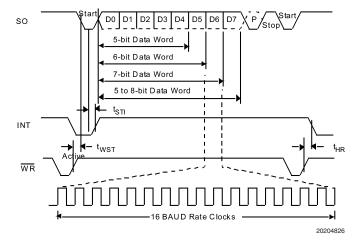

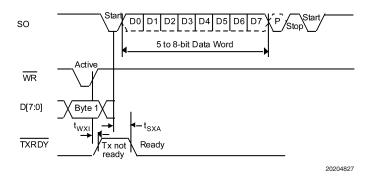

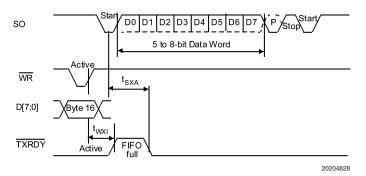

|     | Ena          | 0   | 1 = Enable the interrupt when Tx Holding Register is empty.                                                     |